10월 11일

조합논리회로 Combinational Logic Circuit

기초로 Gate를 다뤘음 (and, or,m not, exor etc)

나아가 Decoder, MUX ... 등을 이용해서 가산기, 감산기를 만들었음.

스위치, Led, Seven segment로 출력을 확인했음. 한계점은 한 자릿수만 출력한다는 것.

--> 4 자릿수를 표현하려면 잔상을 이용해야 함. c 언어 때는 INT를 이용해 주기마다 자릿수를 옮겨서 출력을 진행했음.

FPGA에서 자체적으로 처리하기 위해 알아야 될 개념 : 순차논리회로

--------

순차논리회로 Sequential Logic Circuit

메모리 기능을 가지고 있음. == 과거의 값을 저장하고 있다.(현재와 과거의 값 조합에 따라 결과 출력이 나온다.)

: 책에 보면 여러 목차가 있지만 그 중 카운터가 가장 핵심적임.

(상태, 레지스터, 카운터라는 단어가 나왔는데 이걸 이번 주 동안 할 것.)

기억소자.

DRAM의 기억소자(하드웨어)는 캐패시터임. 충전 여부로 1, 0을 따짐(GB). 하지만 우리가 다루는 레지스터의 기억소자는 게이트의 조합으로 만들어짐. 즉, 트랜지스터(아마 FET)임(대부분 KB, MB).

가장 기본은 Latch이고, 동기화 기능이 들어간 게 Flip Flop임.

: 동기는 어떤 동작기준이 있고 그에 맞춰 행동한다는 것이다. 여기서 말하는 기준은 클럭이 된다.

S R Latch

사진 출처

https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=lagrange0115&logNo=220722338106

SR 래치 - SR latch

래치(latch) 또는 플립플롭(flip-flop)은 1비트의 정보를 보관 또는 유지할 수 있는 회로이며 sequential l...

blog.naver.com

| A | B | OR | NOR |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

| S | R | Q | ~Q |

| 0 | 0 | 유 | 지 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 불 | 능 |

0 1의 경우 R 1이기 때문에 Q는 무조건 0 따라서 ~Q는 0 0조합으로 1이 됨.

1 0 --> ~Q 0 따라서 0 0조합으로 Q가 1

따라서 두 경우만 보면 S와 Q가 동일하다.(이때 출력값은 Q로 본다. ~Q는 신경 안 씀) 이러하여 Reset, Set이라고 한다.

1) Q 출력 ~Q출력이 0 1이라고 하자

2) R S 입력은 0 0이라고 하자.

3) R 0 1 --> 0(Q), S 0 0 --> 1(~Q)

따라서 출력값은 그대로 나온다. 그렇기에 유지다.

1) Q 출력 ~Q출력이 0 1이라고 하자

2) R S 입력은 1 1이라고 하자.

3) R 1 1 --> 0(Q), S 0 1 --> 0(~Q)

이때 전제조건이 있음. Q와 ~Q는 반대여야 함. 따라서 불능이다.

--------

| A | B | and | nand |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

| S | R | Q | ~Q |

| 0 | 0 | 불 | 능 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 유 | 지 |

----

(NOR Latch가 default)

정확히 같이 S R이 0이 들어가야 유지가 됨. 시간차가 있다면 유지가 될 수도, 값이 바뀔 수도 있음. 치명적이 한계.

-->

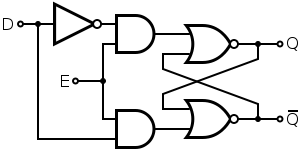

Gated - Latch : 여기서 말하는 gate는 enable을 의미.

그림 출처

https://ko.wikipedia.org/wiki/%ED%94%8C%EB%A6%BD%ED%94%8C%EB%A1%AD

플립플롭 - 위키백과, 우리 모두의 백과사전

위키백과, 우리 모두의 백과사전. R1, R2 = 1 kΩ, R3, R4 = 10 kΩ 플립플롭 또는 래치(영어: flip-flop 또는 latch)는 전자공학에서 1 비트의 정보를 보관, 유지할 수 있는 회로이며 순차 회로의 기본요소이

ko.wikipedia.org

enable에 not gate가 있다고 생각하자.

| G | S | R | Q | ~Q |

| 1 | x | x | 유 | 지 |

| 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 불 | 능 |

즉, Gate : 0 출력값 유지, 1 : 출력값 변경 --> Low Level Trigger(변경되는 게 동작되는 기준 <-> High Level Trigger)

En에 cp(clock pulse)를 줄 수 있다.

이렇게 보고 나니 S R이 다른 경우만 쓰게 됨. --> D Gated Latch

하나의 출력으로 S R 대입

| CP(enable) | D | Q |

| 0 | x | 유지 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

---

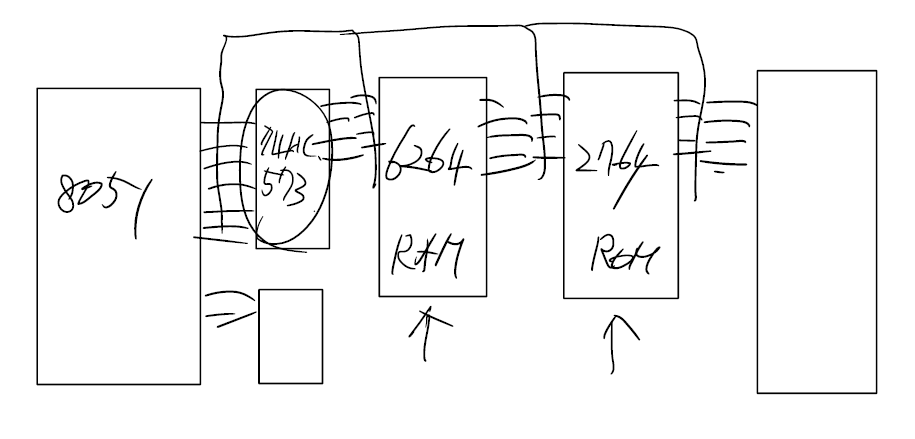

기존 프로젝트에서 Latch를 썼었음. 전자 회로 때 했던 부분인데 회로도에서만 설명하고, 실 부품은 딱히 특정하지 않았는데 74HC573을 썼다고 한다.

---

Gated Latch / Filp Flop

-High/Low Level Trigger : Latch

-High/Low Edge Trigger : Flip Flop(F/F)

Gated latch도 clock이 있기 때문에 clock 차이로 latch, flip flop이 다른 게 아님. level과 edge 차이로 말해야 함.

Master - Slave Latch

Low Edge Trigger, Low active

CP와 D1을 비교해 Q1이 나오고, ~CP와 Q1을 비교하면 Q2가 나오는데 결과적으로, falling edge일 때의 D1 값이 나온다는 걸 알 수 있다.

High Edge Trigger(Rising Edge Trigger)가 되길 원하면 아래 그림처럼 not gate를 앞에 달면 됨.

Flip Flop은 동기화 측면에서 유리함. Latch는 어떤 순간이 아니라 기간을 가지고 따짐. 오류의 여지가 더 많음.

이때, 근본적으로 가지는 오류가 있음.

propagation delay time : 입력과 출력 사이의 delay. (D1과 Q2 사이에서의)

그래서 edge와 high low 변경 시점이 정확히 겹치면 오차가 발생한다.

이 오류를 방지하기 위해, Hold Time, Setup Time이 존재한다. hold time과 setup time은 곧, MCU가 가지는 최대 clock의 속도 제한에 영향을 미친다.

**---------------

다시 복습 필요한 부분.

T : Toggle Flip Flop

JK : SR의 경우 불능이 존재함. 이 부분을 해결한 게 JK Flip Flop.

(제대로 찾아봐야겠음)

단순 D 설명

https://m.blog.naver.com/hafs_snu/221277740243

[대학교 디지털시스템] 래치(Latch)/플립플롭(Flip-flop)

By 루두두 안녕하세요, 루두두입니다. 여러분 오랜만이에요!! 언제나 그렇듯 공부, 또 공부합시다. 오늘은...

blog.naver.com

--------

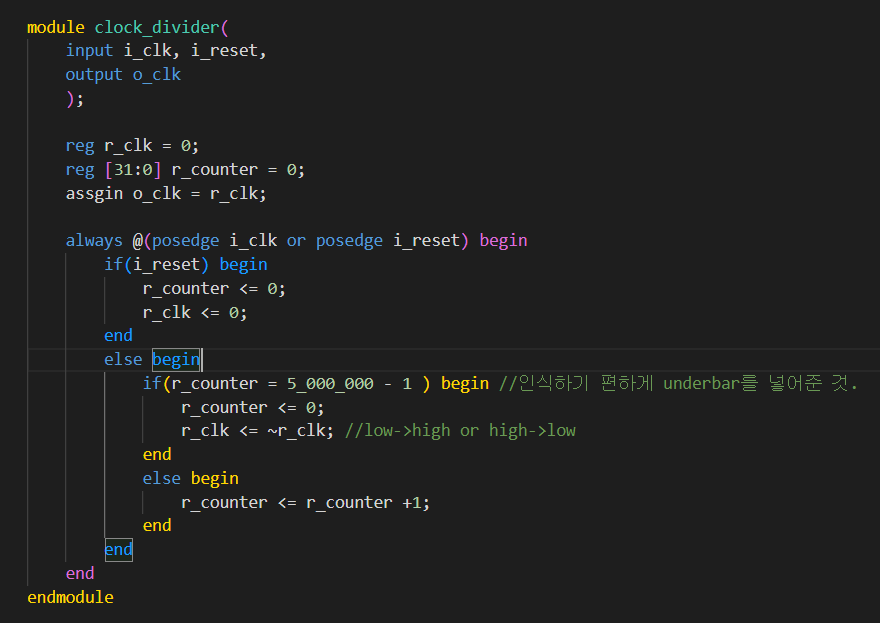

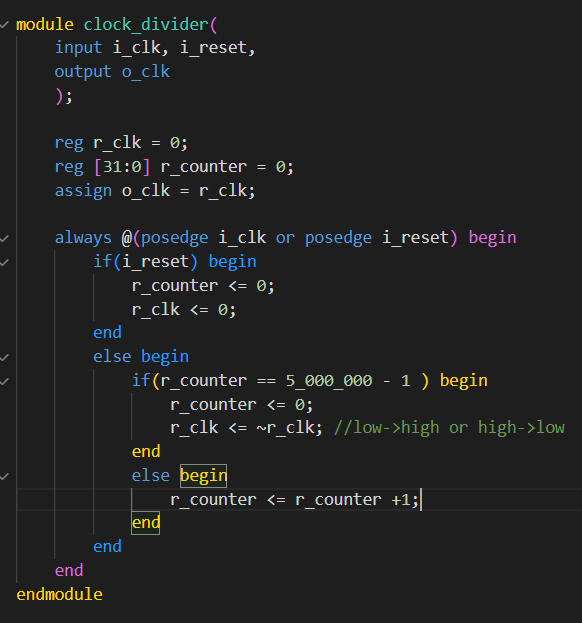

외부 clock에서 timer/counter가 중심.

FPGA는 너무 빠르다. prescaler로 다루기 적당하게 단위를 바꿈.

----**

Led를 3개로 줄이고 다시 표현하자면 다음과 같다.

아래는 bitstream generate을 진행하니까 출력된 메시지다. 그에 맞게 constraints 수정하면 된다.

[Place 30-574] Poor placement for routing between an IO pin and BUFG. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets i_btn_IBUF] >

i_btn_IBUF_inst (IBUF.O) is locked to IOB_X0Y15

and i_btn_IBUF_BUFG_inst (BUFG.I) is provisionally placed by clockplacer on BUFGCTRL_X0Y0

[Place 30-99] Placer failed with error: 'IO Clock Placer failed'

Please review all ERROR, CRITICAL WARNING, and WARNING messages during placement to understand the cause for failure.

[Common 17-69] Command failed: Placer could not place all instances

https://youtube.com/shorts/qXlMcVpAEdA?feature=share

-----------------

button을 눌러서 인식을 시켰는데, 이제는 진짜 외부 클럭을 카운팅해보자.

r_counter가 10,000,000/2인 이유

조건에 도달하면 r_clk은 toggle되면서 edge가 발생한다. 우리 기준으로 clock은 한 번 올라가고 다시 내려와야 제대로 된 하나의 사이클이다. 즉, 두 번 toggle이 돼야 한 클럭이 된다.

## Clock signal

set_property -dict { PACKAGE_PIN W5 IOSTANDARD LVCMOS33 } [get_ports { i_clk }]; #IO_L12P_T1_MRCC_34 ,Sch=CLK100MHZ

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports sysclk]

-----------

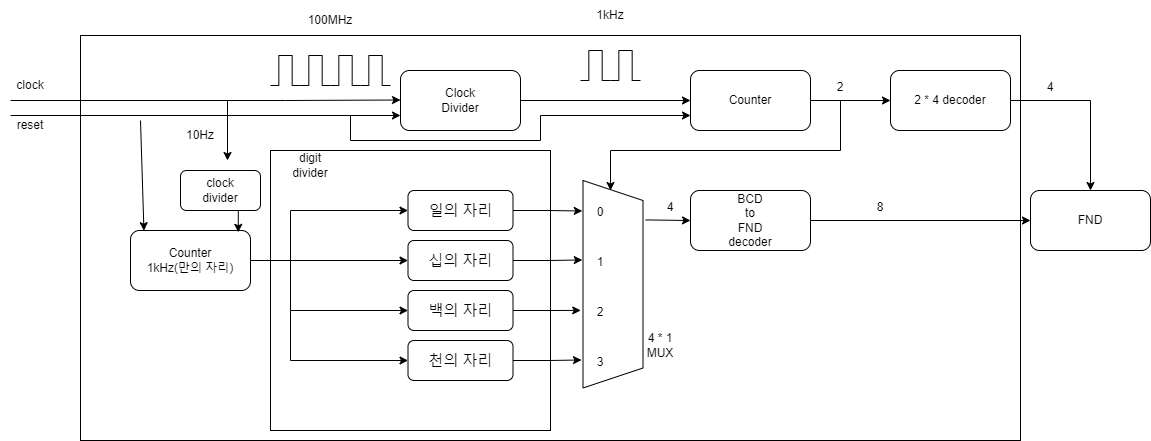

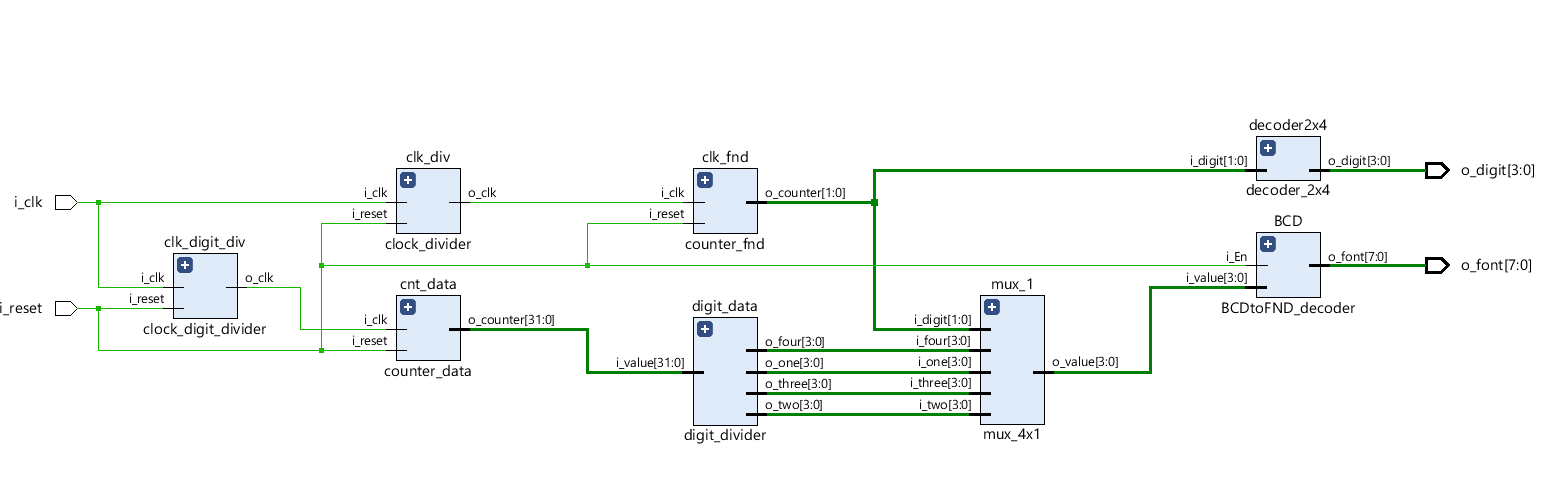

4FND

드디어 자릿수 변경을 하며 출력하는 FND를 진행해볼 것이다.

특별히 어렵다기 보다는 i_clk 인수를 받고 원하는 clock 수에 도달해 i_clk 값 전달이 발생하면, counter 값에 변화가 생기도록 always문을 작성한다는 개념만 제대로 잡혀있으면 된다.

https://github.com/316415/FND_display_used_INT.git

GitHub - 316415/FND_display_used_INT: It's time counter that counts every 0.1s. And I use the interrupt. Design is made by Seque

It's time counter that counts every 0.1s. And I use the interrupt. Design is made by Sequential Logic Circuit. - GitHub - 316415/FND_display_used_INT: It's time counter that counts every 0...

github.com

https://youtube.com/shorts/GqGm-hY9P_I?feature=share

------

git push error 해결법

git push origin main --allow-unrelated-histories